# Virtual Processor based on Hybrid Processor

Akram Saleh Almansoub<sup>1</sup>, Qi Deyu<sup>2</sup>, Fares Aqlan<sup>3</sup> and Abdullah Alqwbani<sup>4</sup>

<sup>1</sup> South China University of Technology

*Received: 12 December 2018 Accepted: 4 January 2019 Published: 15 January 2019*

5

## Abstract

This proposal presents a robust method through which virtualization can be optimized by the use of a hybrid processor. The discourse acknowledges that virtualization has become a key constituent of machine processing and efficiency through building virtual machine clusters that can be universally integrated to harness the utilization of hardware computing resources. As observed in low-level computing paradigms, the traditional x86 architecture was only capable of classical trapping to deploy virtualization, yielding para-virtualization. In response, virtual processors based on hybrid processors with hardware-assisted paging enables the handling of foreign Memory Management Unit (MMU) operations and translates the corresponding physical address to actual machine-controlled dynamic addresses, improving memory bound executions as well as the overall output of the HVM. This architecture derives a more powerful utility from the compromised architecture whereby the kernel space while the user space resides in the same privilege ring. Even though myriad hybrid architectures exist, the ultimate objective of this proposal is to satisfy one intrinsic feature: incorporate superiority behavior of the hardwareassisted virtualization.

21

---

22 *Index terms*— virtual processor, hybrid processor, algorithm, virtualization, CPU machine

## 1 Introduction

Virtualization technology has recovered a substantial devotion for some time in computer system designing. Virtual Machines found a path of arrangement for encompassing latest server consolidations, secure computing and also transparent migration, and list the current to a system that maintains capability of the latest operating systems. In this analysis, the method of virtual processor based on hybrid process is seen in the presentation of computer systems that change level of parallel in multiple threads per node. The major goal of this research to analysis a virtual processor based on hybrid process. The research will further focus on the software and hardware processing on virtual processor based on hybrid process for a computer and multispectral methods. To arrive at the final goal of the research, the paper will be divided into three parts. The first part will be an analysis of a virtual processor, the second part will be a presentation on hybrid processor and the third will be an analysis of virtual processsor based on hybrid process. If a virtual processor has a hybrid system of plurality storage device attached, a thread can be utilized in hybrid system/CPU. Therefore, a task could heavily occupy the available hardware in the virtual system.

## 2 II. related work

According to Hoff beck, et. al "on a similar accession, the increasing thickness of power and wickedness o the latest servers has also projected numerous methods to Operating system directed control on energy consumption of the computer" (78). Though the energy management approaches are developed for legacy operating systems with a monolithic kernel. In most cases, monolithic kernels possess control of all the hardware devices and their mode of operation. It controls both energy ingesting and device activity to meet limitations of energy. Monolithic

## 2 II. RELATED WORK

---

42 kernels controls the low in the system by tracing the power ingesting at individual level and also limit its specific

43 sill in the process of device allocation to attain inclusive energy management (79) [1].

44 Virtualization is an abstraction layer (SW) that furs physical features of computing platform from the users,

45 in its place showing another intangible, rivaled computing platform. Machine virtualization is about the creation

46 and management of VMs on a "real" machine. For example Java Virtual Machine to accept java byte code in

47 the form .class files. Virtual PC allows Windows app to be run on Mac/PowerPC, Sun PC SW emulates a PC

48 how environment on Solaris/SPARC(Zhang, W Liang, and H Qiao, 195) [2].

49 A virtual CPU is allocated to a virtual machine. Virtual machines are automatically allocated a virtual central

50 processing unit each. The CPU scheduler allocates execution settings in case the physical hosts possess numerous

51 CPU cores. The vCPU becomes a sequence of time slots on logical processors (Katz, 6). It is significant for the

52 administrator to comprehend the cloud of the usage of vCPU in an invoice since the dispensation time is billable.

53 Adding more vCPU insignificantly advance the performance since the number when the number vCPUs raises,

54 it gets hard for the scheduler to arrange many on the same CPUs (Chritoph et. al, 65) [3].

55 In most cases, vCPUs are a source of the symmetric multi-processing (SMP) multi-threaded model of the

56 computer. SMP allows threads to pass across numerous logical cores to advance performance of similar tasks.

57 vCPUs also on the same note allows multitasking to take place consecutively in physical environment V A

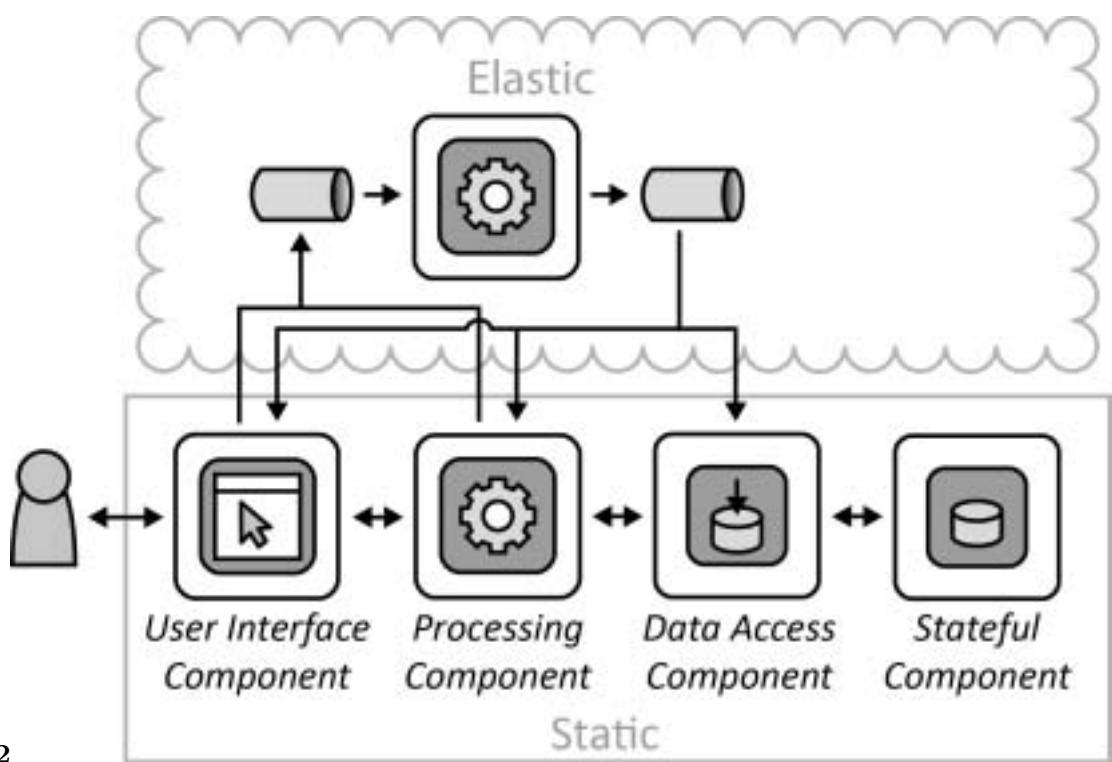

58 Distributed Application provides processing functionality that practice varied workload behavior. The user

59 group retrieving the application is, thus, probable in size, but accesses the functions given by the application

60 inversely. Whereas most of the purposes are used correspondingly over time and, thus, undergo Static Workload,

61 some Processing Components experience Periodic Workload, Changeable Workload, or Unceasingly Changing

62 Workload (Lesnik, et.al, 1524).The Processing Mechanisms experiencing changing workloads are provisioned in an

63 elastic cloud. Loose Connection is ensured by switching information between the hosting settings asynchronously

64 via messages.

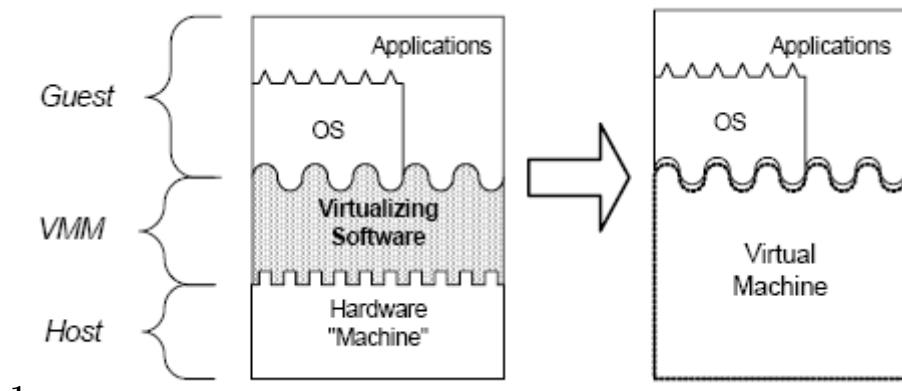

65 A VM performs SW in the similar way as the machine for which the SW was established. VM is applied as a

66 mixture of actual machine and virtualizing software. The VM can have diverse resources diverse from the real

67 machine either in quantity or type (cpu, mem, I/O, etc). A VM frequently offers a less perf than the same actual

68 machine operating the same SW.

69 Use of actual system calls to perform the functions given by VM instructions. Mapping of virtual state to

70 actual resources. VM has two types which include: System VM operating as OS and process VM operating as a

71 user process. VM monitor provide a total environment backup of various user processes, offering them entree to

72 I/O devices, and acknowledge GUI of the desktop (Babic, Matej, 37) [4].

73 In any case, when running an operating system is installed on the server, the system always analyses the overall

74 number of operations it can manage simultaneously by encompassing the total number of processors which are

75 on the serve. In a case when operating systems are installed on the like which has eight or ten processors, every

76 processor will have to manage two systems simultaneously. The system wills in total manage sixteen and twenty

77 operations at a go consecutively. In the same way when an operating system is installed on a logical panel that

78 accepts devoted processors, the operation system will then examine the total number/weight of the processes

79 which it can concomitantly manage through examining the total number of devoted processors that are given to

80 partition. In both scenarios, the system in operation can end lessly examine the total operations it can handle

81 by including the whole number of processors that can be accessible ??Babic, ??atej, ??0) [4].

82 According to Blanchet and Dupouy, "When an operation system is inserted on a sound partition that allows

83 joint processes, the system will have to examine the slight number from the total number of processing units and

84 are availed to a portion" (179) [5]. The server represents the processing power obtainable to the operating system

85 on the while number of processors. The scenario permits the computation of the total number of multiple existing

86 operations that it can handle. Virtual processor is referred as a symbol of physical processor of a working system

87 of logical par that permits joint processors. Processing units are coincidently allocated by the server firmware

88 among the virtual processors allocated to reasonable part. In a given scenario when a logical partition entails one

89 point eight processing and two processors, it will be discovered that each virtual processor will have zero point

90 nine (0.9) processing units helping its workload Virtual processor has limitation of processing units. I a normal

91 case, each virtual processor should only have 0.1. When firmware is FW760 or more, the minimum number of

92 processing units will also decrease to 0.05. The extreme number of processing units each processor should have is

93 1.00. This amounts to a logical partition that can employ more processing units as compared to virtual processors

94 which is available (Morris and Detlefsen, 67).

95 If the total number of virtual processor nearly to number of processing units available to the logical part,

96 a logical partition always works very excellent. The enables the system of operation to accomplish a workload

97 on logical partition efficiently. In certain scenarios, you can also be in place to increase system presentation

98 somewhat b increasing the total number of virtual processors. If you upsurge the number of operations that

99 operate concomitantly. On the same note, though you can upsurge the number of virtual processors minus

100 altering the number of processing units, the restrictions of every operation operates will reduce. It is impossible

101 for the running system to move processing power between processing powers dividing among processes the poses

102 if the power of dividing among numerous virtual processors.

---

103 **3 III.**

104 **4 Hybrid Virtual Processor**

105 System virtualization is a technology which can divide a single host (e.g., computer, server, etc.), into multiple

106 parts, or partitions, each running a separate instance, or image, of a working system. Instances of functioning

107 systems or partitions are separate, or isolated, from each other in some ways. For example, the partitions

108 have separate file systems, separate users, separate applications, and separate processes Bi and Liang, 197) [6].

109 However, the partitions may also share some resources of the host. For example, the partitions can share the

110 memory, the kernel, the processors, the hard drives, and/or other software, firmware, and/or hardware of the

111 hos. Thus, each partition or instance of the operating system can look and feel like a separate server or machine

112 from the perspective of its users. These instances are commonly referred to as "virtual" or "virtualized" machine

113 and each partition may be referred to as a logical partition (LPAR) ??198).

114 One server or data processing system can generally host a number of LPARs. These LPARs generally have

115 virtual resources assigned to them (e.g., virtual processors) which provide an abstraction of the physical resource

116 from which it is based (e.g., the physical processor). For example, a virtual resource may be considered a logical

117 entity that is backed up by the physical entity. In a dedicated mode of LPAR operation, physical resources are

118 assigned as a whole to an LPAR such that the assigned physical resources are not shared by other LPARs (Hoff

119 beck, et.al, 78). In a shared mode of LPAR operation, the physical resources are part of a pool of resources which

120 are shared among the LPARs. Additionally, LPARs can be configured to have a certain entitlement capacity

121 representing a guaranteed physical resource capacity for the LPAR. LPARs may also be configured as capped or

122 uncapped. In a capped mode, the resource capacity for the LPAR is capped at some value (e.g., its entitlement

123 capacity). In an opened style, LPAR would surpass its entitlement capability after other shared resources are in

124 place.

125 Cai, and Yan note that "Field programmable gate arrays (FPGAs) have been considered for either augmenting

126 or replacing microprocessors in order to expand the limitations posed by the arithmetic logic units" (1005)

127 [9]. Wholesale replacement of microprocessors with FPGAs generally requires the entire recoding of operating

128 systems. On the other hand, redesigning microprocessors to include FPGAlike architecture presents its own set

129 of design errors.

130 According to Wang and Chen "Bywords of the current evelation give a technique, structure and processor

131 program merchandise for hybrid virtual machine configuration management" (1097) [7]. For example, in some

132 embodiments, the method and technique includes: assigning to a major set of virtual properties linked with

133 enabled possessions of a virtual apparatus a first priority; giving to a second set of virtual resources associated

134 with the virtual appliance a second useless than the first use, where the first and seconds types when joined

135 surpass the permitted resources for the virtual machine; charting the first types of virtual resources to a first

136 known resource of a pool of shared physical resources assignable to the first and second sets of virtual properties,

137 whereas the initial physical resource includes a anticipate dempathyequal to a second physical resource assigned

138 to the virtual machine; and differently assigning the first physical resource to the first set of virtual resources

139 (Blanchet and Dupouy, 178) [5].

140 In accordance with the present invention, a hybrid, modular processor package and method for developing

141 a hybrid, modular data processing package from microprocessor and field programmable gate array (FPGA)

142 technology combines a microprocessor, an FPGA, and a modular controller chip in order to obtain enhanced

143 performance over that of the microprocessor (Zhang, W Liang, and H Qiao, 193) [2]. The combination of the

144 microprocessor, FPGA, and controller chips is effected by identifying and selectively routing the noncontrol

145 pins of the respective chips in parallel to the hybrid package pins and routing respective control pins of the

146 microprocessor and FPGA through the controller pins. The controller chip emulates the behavior of the selected

147 microprocessor bus interface and provides a set of services to the FPGA, such as configuration and memory

148 management. By creating a standard interface to the FPGA and different microprocessor bus interfaces, a

149 configuration code compatible family of computing devices can be created.

150 According to Salem, et al "Personifications of the current disclosure allow improved empathy levels keep

151 maintained to physical resources in a shared resource pool environment" (5) [8]. Embodiments of the present

152 disclosure utilize a prioritization scheme to assign a higher priority to entitlement virtual resources than to virtual

153 resources utilizing uncapped excess resources of the pool (Cai, and Yan, 1003) [9].

154 Physical resources having a desired or greatest affinity level to a physical resource of interest are mapped to

155 the high priority virtual resources. In response to the dispatch of a high priority virtual resource, a physical

156 resource allocation preference is given to the high priority virtual resource over a virtual resource that may be

157 utilizing the mapped physical resource in an uncapped, shared mode.

158 Venkata, et al note that "Features of the current disclosure can be personified as a system after being

159 acknowledged by a given skill. Consequently, features of the current disclosure can take the form of a complete

160 hardware personification, an embodiment joining features of hardware and software, a total software embodiment

161 like circuit, module or system" (4748) [10]. On the same note, the new disclosure can take the form of processor

162 program product personified in additional clear mediums of computers taking computer clear program code

163 personified

164 The mixture of more processor usable or computer readable mediums is utilized. Computer readable medium

165 is a computer legible signal medium stowing medium. In any case the processor readable storage medium is

166 electronic, inferred, optical, magnetic, apparatus, devices semiconductors system. Other examples include: an

167 electric having more wires, portable computer diskette, flash memory, hard disk, optical fiber, optical storage

168 device, magnetic storage compact disc read only memory mention but a few. A computer has a readable storage

169 medium which is a tangible medium that stores program for use by an instruction execution device (Hewlett and

170 Wright, 983) [11].

171 Computer readable signal medium entails a spread data with system readable program code personalized

172 within. This include: part of a carrier wave. Propagated signals of this kind are of different types including optical,

173 electro-magnetic and many others. A virtual processor decipherable indication medium is in any computer clear

174 medium that is not a virtual processor readable storage medium band that connect and conveyance a program for

175 use by linking with a training device and execution system. A program core put on a processor legible medium

176 is comminuted using a suitable medium like RF, wireless, optical fibre cable and a combination of all the above

177 (Zhang, Liang and Qiao, 190) [2].

178 Lesnik et al assert that " features of the current disclosure are labeled with reference to flowchart and diagram

179 of devise, gear, computer program products and system as paper the personifications of the disclosure" (1523). It

180 is understood that the flow of the flowchart picture, the flowchart diagram, illustration and ampule be applied by

181 computer program instructions. These instruction of the processor are given to a computer for a distinct purpose

182 and any other programmable data processing device to give out a machine, such that the commands that execute

183 via a computer devices and programmable data processing device which create ways of applying the functions

184 mentioned in the flowchart (1525).

185 According to Babic, Matej "In a method for providing concurrent access to virtual memory data structures,

186 a lock bit for locking a virtual page data structure is provided in a page table entry of a page table" (38). The

187 page table is configured to map virtual pages to physical pages. Then, a first thread specifying an operation on

188 the virtual page data structure is received. The first thread is provided exclusive access to the virtual page data

189 structure by setting the lock bit in the page table entry such that other threads are prevented from accessing

190 the virtual page data structure. A wait bit also may be provided in the page table entry to indicate that one or

191 more of the other threads are in a wait queue when the first thread contains limited access to the data program.

192 When the first thread no longer needs exclusive access to the data structure, a second thread is selected from

193 among the other threads and is provided with limited access to the data configuration (39).

194 The computer program directives put onto programmable data dispensation apparatus to source a sequences

195 of the ladder of operation to be done on the computer so as to yield a programmable device

## 196 5 Virtual Processor Based on Hybrid Processor

197 A computer program has a code for performing out virtual processes for structures of the current disclosure is

198 shown in various of programming languages with a target of programming languages like conventional technical

199 programming languages (comparable software design languages and Cprogramming language), Smalltalk and

200 Java. The program code performs completely on the computer of the user, partly on the computer of the used

201 as software set, partially on a remote processor and on a remote processor completely. According to Blanchet

202 and Depouy " In a given situation, the remote computer can be linked to the user of the computer over a given

203 network, a local area network or far reaching network and by linking can be made to an outside virtual processor

204 for example over the internet employing internet service distributor [5].

205 processes for applying the acts started in the flowchart (Dhas, and Kumanan, 9) [12].

206 A virtual processor has a reconfigurable, programmable logic matrix array for processing data in accord

207 with a hardware encoded algorithm, a memory for storing a number of hardware configuration records for the

208 programmable logic matrix array, each configuration file for programming an algorithm to be performed by the

209 matrix array, an input/output bus for providing data to the matrix array for dispensation and for procurement

210 treated data from the matrix array, a memory expedient for storing data, a VPM regulator for monitoring the

211 overall procedure of the virtual processor plus giving operation arrangement maps, providing parameters for

212 precise operations, and offering status information, a data bus manager for controlling the flow of the data to the

213 matrix array for processing, and also configuration supervising the order of reconfiguration of the matrix array

214 to route data by a specific order of algorithms ??Rodic, ??eteret et al, ??0)[13].

215 The figure below illustrates a computer system including a hybrid data processor.

216 There block diagram of data processing system 100 which includes hybrid, modular data processor 101. Hybrid

217 data processor 101 connects conventionally to a conventional memory unit 103 through data/control Input/output

218 (I/O) buses 105. Address controller 107 receives address and control instruction information from processor 101

219 over buses 109, and conventionally controls the addressing of data within memory device 103 by hybrid data

220 processor 101 utilizing buses 110.

221 A computer has two forms of storages which include: the Primary storage and secondary storage. The

222 virtual processor closely relates with the major memory, involving the instructions and data. In examining the

223 preparation of the CPU in the virtual machine monitors hypothetically. A virtual processor memory temporally

224 holds data when a virtual processor processes a program. Secondary program clasps permanent and semi-

225 permanent data on the outward magnetic medium. There are two kinds of virtual machines in the system which

226 includes: the highthroughput and the concurrent. The virtual machine is put as synchronized type when all of

227 the workload is synchronized submissions so as to minimize the cost of synchronization.

228 The main storage which is also referred to as memory which also has different terms like main memory, main

229 storage, internal storage, and primary memory. The terms are used interchangeably by computer specialists

230 on those well versed with computer programs. Memory is portion of the virtual processor that grips data and

231 guidelines for dispensation. Keeping items in retention when the database is not operating feasible. Though

232 the memory is associated with the central processing unit closely; it is distinct from other items. Memory keeps

233 program and the command in the whole process of operation.

234 To manage the issue, hybrid scheduling framework is given for CPU management in the VMM to adjust to

235 the variety of VMs running concurrently on the machine.

236 However, implementation of a hybrid scheduler was founded on Xen and the outcome show that hybrid CPU

237 management technique is also predictable to alleviate the negative impact of the virtualization on synchronization

238 and advance the performance of synchronized application in the virtualized scheme in upholding the presentation

239 of high all through the application (Stampar, Simon, et al, 113) [14].

240 According to Zitter, Ilya, and Aimee Hoeve "With virtualization skill, the functionality of several standalone

241 processor systems can be combined into a sole hardware processor, to promote effective usage of the hardware

242 whereas reducing power depletion" (78) ??15]. As a consequence, virtualization is a significant brick for

243 structuring the cloud substructure for example the computer elastic of Amazon. Currently, a virtual machine

244 monitor (VMM) is sedentary between the working system level and the hardware level in the virtualized system,

245 instances of system virtualization comprise Xen, Hyper-V, VMware, Virtual Box and KVM. Diverse from the

246 outdated system software stack.

## 247 6 IV.

## 248 7 Experiments and Analysis a) Virtual processor and hybrid 249 processor

250 The technology of virtualization creates it possible that different guest functional system operate on virtual

251 machine. The virtual processor based on Table ??: Format hybrid data processor maintaining part of the system

252 consuming time to the weight of operation, exhausting the system volume. Though this type of arrangement

253 makes it worse in the performance if at all the virtual machine which is aligned to hybrid system of operation

254 can be used to finalize the applications of equal programs (McDowall, Wil, 63) [16].

255 Preparation of a synchronous virtual processor based on hybrid process preparation strategy leads to enough

256 physical virtual time when the system workload is synchronized. The diskettes and CD-ROM disk are secondary

257 storages in giving a hybrid development framework for the virtual processor setting up a machine up in a virtual

258 monitor. The storage device is put as a high throughput from as the default then the virtual traits of lesser

259 storage system control the as data is prearranged. In implementing the hybrid development framework built

260 on Xen, the recital of the presented arrangement framework and plan based on the multicore stage and the

261 test portrays the scheduling framework and strategy to advance the performance of the virtual machine system

262 (Leupers, Eeckhout, et al, 718) [17].

263 Blanchet and Dupouy note that "Virtual machines (VMs) with a diversity of assignments may run

264 concurrently on a virtual machine in the cloud platform" (1216). The arrangement algorithm used in Xen

265 schedules virtual hybrid based processor of a VM asynchronously and assurances the quantity of the processor

266 time allocated to the VM. As a significant keystone for clouds, virtualization plays a vigorous role in building

267 this developing of both hybrid and virtual processor (1217) [5].

268 Blanchet, Gerard et al note that "when workloads in VMs are concurrent applications like multithreaded

269 programs with the synchronization process, it has been established that this type in the VMM can decrease

270 the presentation, due to the undesirable effect of virtualization on synchronization" (178). This proportional

271 sharing (PS) method is helpful as it shortens the application of CPU arrangement in the virtual machine monitor

272 (VMM), and can convey nearnative performance for certain workloads. Prior to the executing of instruction,

273 processor instructions and data has to be put in the memory from an input system and a lesser storage system

274 (the procedure is in addition complex by the element that, as noted earlier, the data will automatically make a

275 provisional stop in a record) (180) [5].

276 According to Acosta, Eric, and Alan Liu "A virtual hybrid based processor system using a special instruction

277 inserted into a thread (virtual processor) at a selected point to trigger an immediate thread change (i.e., transfer

278 of virtual processor control to hybrid process)" (1099) ??18]. When the virtual processor processes a hybrid

279 instruction, the task thread surrenders control of the virtual processor, and an otherwise idle thread is selected

280 by a thread scheduling mechanism of the MVP system for loading into the physical processor. V.

## 281 8 Conclusion

282 Virtualization technology has improved a large devotion for some time in computer system designing. Virtual

283 Machines found a passageway of collection for about latest server consolidations, secure computing and also

284 transparent migration, and list the current to a system that maintains the capability of the latest operating

## 8 CONCLUSION

---

systems. In this analysis, the method of virtual processor based on the hybrid process is seen in the presentation of computer systems that change the level of parallel in multiple threads per node. The major goal of this research to analysis a virtual processor based on hybrid process. The research further focused on the software and hardware processing on virtual processor based on the hybrid process for a computer and multispectral methods. We arrived at the final goal of the research, the paper divided into three parts. The first part I an analysis of a virtual processor, the second part I displayed on the hybrid processor and the third part I analyzed of virtual processor based on hybrid process. If a virtual processor has a hybrid system of plurality storage device attached, a thread can be utilized in hybrid system/CPU. Therefore, a task could heavily occupy the available hardware in the virtual system. System virtualization is a technology which can divide a single host (e.g., computer, server, etc.), into multiple parts, or partitions, each running a separate instance, or image, of a working system. Instances of functioning systems or partitions are separate, or isolated, from each other in some ways.

A computer has two forms of storage which include: the Primary storage and secondary storage. The virtual processor closely relates with the major memory, involving the instructions and data. In examining the preparation of the CPU in the virtual machine monitors hypothetically.

Preparation of a synchronous virtual processor based on hybrid process preparation strategy leads to <sup>1</sup>

Figure 1: Fig. 1 :

Figure 2: Fig. 2 :

2

Figure 3: Table 2 :

---

301 enough physical virtual time when the system workload is synchronized. The diskettes and CD-ROM disk are

302 secondary storages in giving a hybrid development framework for the virtual processor setting up a machine up

303 in a virtual monitor.

304 [ Christoph () , Christoph . *Cloud Computing Patterns*. Springer 2014. p. . (Print)

305 [Acosta and Liu () 'A Pipeline Virtual Environment Architecture for Multicore Processor Systems'. Eric Acosta

306 , Alan Liu . *The Visual Computer* 2012. 28 p. . (Print)

307 [Wang () 'A System-Level Network Virtual Platform for IPsec Processor Development'. Chen Wang . *Ieice

308 Transactions on Information and Systems* 2013. 96 p. .

309 [Venkata () 'Design and Implementation of Scheduler for Virtual File Systems in Shared Memory Multi-Core

310 Processor Using Arm-Fl2440'. Venkata . *International Journal of Control Theory and Applications* 2016. 9 p.

311 . (Print)

312 [Hewlett et al. () 'Dynamic Monitoring Efficiency of Computer Processor Virtual Memory Management Data

313 Structures'. Wright ; Hewlett , R Company , Wright . *Research Disclosure* 2012. 2012. p. 983. (Print) (Research

314 Disclosure.)

315 [McDowall () 'Exploring Possible Transition Pathways for Hydrogen Energy: A Hybrid Approach Using Socio-

316 Technical Scenarios and Energy System Modelling'. Will McDowall . *Futures* 2014. 63. (Print)

317 [Zitter and Hoeve () *Hybrid Learning Environments: Merging Learning and Work Processes to Facilitate

318 Knowledge Integration and Transitions*, Ilya Zitter , Aimee Hoeve . 2012. (Print)

319 [Hoffbeck () 'Interfacing Matlab with a Parallel Virtual Processor for Matrix Algorithms'. Hoffbeck . *The Journal

320 of Systems & Software* 2001. 56 p. . (Print)

321 [Cai () 'Labview-based Parallel Optimization of Networked Virtual Test System in Multi -Core Processor

322 Environment'. Yan Cai . *Advanced Materials Research* 2012. p. . (Print)

323 [Babic () 'New Hybrid System Using in Modeling Process of Hardening with Intelligent System'. Matej Babic .

324 *Acta Mechanica Slovaca* 2016. 20 p. . (Print)

325 [Zhang () 'Processor Coalition Algorithm for Virtual Routers on a Multiprocessor System'. Liang Zhang , Qiao

326 . *Advances in Information Sciences and Service Sciences*, 2012. 4 p. . (Print)

327 [Bi () 'Processor Coalition Algorithm for Virtual Routers on a Multiprocessor System'. Liang Bi . *Advances in

328 Information Sciences and Service Sciences*, 2012. 4 p. . (Print)

329 [Rodic () 'Study of a Sol-Gel Process in the Preparation of Hybrid Coatings for Corrosion Protection Using Ftir

330 and [sup] 1h Nmr Methods'. Peteret Rodic . *Journal of Non-Crystalline Solids* 2014. 2013. 59 p. . (Print 15.

331 Stampar) (Strojnicki Vestnik. Print)

332 [Salem () 'The Development of Body-Powered Prosthetic Hand Controlled by Emg Signals Using Dsp Processor

333 with Virtual Prosthesis Implementation'. Salem . *Conference Papers in Engineering* 2013. 2013. 4 p. . (Print)

334 [Blanchet () *Virtual Memory*, Dupouy Blanchet . 2013. p. . (Print)

335 [Blanchet () *Virtual Memory*, Ge?ard Blanchet . 2013. p. . (Print)